## Description and Specialization of Coarse-grained Reconfigurable Architectures

Dissertation

der Fakultät für Informations- und Kognitionswissenschaften der Eberhard-Karls-Universität Tübingen zur Erlangung des Grades eines Doktors der Naturwissenschaften (Dr. rer. nat.)

> vorgelegt von M.Sc. Julio Alexandrino de Oliveira Filho aus Recife, Brasilien

> > Tübingen 2010

Tag de mündlichen Qualifikation:Dekan:1. Berichterstatter:2. Berichterstatter:

10.02.2010Prof. Dr.-Ing. Oliver KohlbacherProf. Dr. Wolfgang RosenstielProf. Dr. Edna Natividade da Silva Barros,UFPE, Brazil

## Danksagung

Ich möchte an dieser Stelle allen herzlich danken, die mich während dieser Zeit auf vielfältiger Weise unterstützt und die zum Gelingen dieser Arbeit beigetragen haben.

Mein besonderer Dank gilt Herrn **Prof. Dr. Wolfgang Rosenstiel** für die wertvolle wissenschaftliche Betreuung, die Bereitstellung einer exzellenten Arbeitsumgebung, sowie die Übernahme der Betreuung dieser Dissertation. Mit seiner Aufgeschlossenheit gegenüber neuen Ideen, seiner Bereitschaft für internationale Kooperationen und seiner wertvollen Kritik hat zu dieser Arbeit wesentlich beigetragen.

Frau **Prof. Dr. Edna Natividade da Silva Barros** danke ich für die Übernahme des Referats dieser Dissertation und ihre sorgfältige Begutachtung der Arbeit.

Diese Arbeit entstand während meiner Tätigkeit als wissenschaftlicher Mitarbeiter im Arbeitsbereich "Technische Informatik" am Wilhelm-Schickard-Institut für Informatik an der Universität Tübingen und ich möchte mich zunächst bei allen Kolleginnen und Kollegen an dieser Universität bedanken. Ganz besonders Dank vor allem dem CRC-Team: **Thomas Schweizer**, **Sven Eisenhardt** und **Tobias Oppold**, die durch zahlreiche Gespräche und Diskussionen hilfreiche Hinweise und Anregungen beigesteuert haben. Für die fruchtbare Zusammenarbeit danke ich noch den Studenten **Stephan Masekowsky** und **Anja Küster**. Für die aktive Revision und Korrektur dieses Dokuments danke ich noch Herrn **Dr. Tommy Kuhn** und **Andreas Bernauer**.

Für die finanzielle Unterstützung, bedanke ich mich bei dem **Alßan Program** - European Union Programme of High Level Scholarships for Latin America (E04D045457BR) und der **Deutschen Forschungsgemeinschaft** - Priority Programm 1148 on Reconfigurable Computing Systems (RO 1030/13-X). Ein weiterer Dank gilt Frau **Margot Reimold** für die administrative Unterstützung hinter den Kulissen.

Mein herzlichster Dank gilt meiner Frau **Suzanne Oliveira-Martens**, die durch sorgfältige Korrekturen und wertvolle Hinweise die Qualität dieses Dokuments deutlich erhöht hat. Ihr noch herzlichen Dank für die ausdauernde Unterstützung und das Verständnis während der arbeitsintensiven Phasen meiner Promotion.

Schließlich danke ich meinen Eltern, **Julio Oliveira** und **Selma Tavares**, die mich während meiner gesamten Studienzeit stets darin bestärkt und unterstützt haben, meinen Weg zu gehen.

Tübingen, January 2009

Julio A. Oliveira Filho

## Contents

| 1. | Intro | oductio  |                                                                  | 1 |

|----|-------|----------|------------------------------------------------------------------|---|

|    | 1.1.  |          |                                                                  | 2 |

|    | 1.2.  | 0        | 1 1                                                              | 3 |

|    |       |          |                                                                  | 3 |

|    |       | 1.2.2.   |                                                                  | 4 |

|    | 1.3.  | Workflo  | ow and organization of this document                             | 5 |

| 2. | Bas   | ics      | 9                                                                | 9 |

|    | 2.1.  | Archite  | cture                                                            | 9 |

|    |       | 2.1.1.   | The CRC Model                                                    | 0 |

|    |       | 2.1.2.   | The CRC Template                                                 | 2 |

|    |       | 2.1.3.   | The CRC Instance                                                 | 4 |

|    |       | 2.1.4.   | The Processing Element                                           |   |

|    |       | 2.1.5.   | The Functional Units                                             |   |

|    | 2.2.  | Applica  | ttion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $15$          | 8 |

|    |       | 2.2.1.   | Application representation                                       | 8 |

|    |       | 2.2.2.   | Application mapping                                              | 1 |

| 3. | Stat  | e of the | Art 2                                                            | 7 |

|    | 3.1.  | Coarse   | grained reconfigurable architectures                             | 7 |

|    |       |          | NEC - DRP                                                        | 7 |

|    |       | 3.1.2.   | Silicon Hive — ULIW                                              | 9 |

|    |       | 3.1.3.   | IMEC — ADRES                                                     | 1 |

|    |       | 3.1.4.   | Weakly Programmable Processor Arrays 34                          | 4 |

|    | 3.2.  | Other W  | Vork                                                             | 6 |

|    |       | 3.2.1.   | KressArray                                                       | 7 |

|    |       | 3.2.2.   | Morphosys                                                        | 7 |

|    |       | 3.2.3.   | Rapport's Kilocore (Piperench)                                   | 8 |

|    |       | 3.2.4.   | Summary                                                          | 8 |

|    | 3.3.  | Evaluat  | ion of the state of the art                                      | 8 |

|    |       | 3.3.1.   | Description of CGRAs                                             | 8 |

|    |       |          | Design and specialization of coarse grained architectures        | 2 |

|    | 3.4.  | Summa    | ry: analogy with the design of application specific processors 4 | 4 |

| 4. | Des   | criptior | of Coarse Grained Arrays 4                                       | 7 |

|    |       | -        | ion and contributions of CGADL                                   |   |

|    | 4.2.  |          | L - Semantics and Syntax                                         |   |

|    |       | 20.101   |                                                                  | 2 |

### Contents

|    |                                            | 4.2.1.                                                                                                                                                                          | The PARAMETER section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51                                                                                                   |

|----|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

|    |                                            | 4.2.2.                                                                                                                                                                          | The PE section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 52                                                                                                   |

|    |                                            | 4.2.3.                                                                                                                                                                          | The ARCH section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 52                                                                                                   |

|    | 4.3.                                       | Estimat                                                                                                                                                                         | ion of hardware costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71                                                                                                   |

|    |                                            | 4.3.1.                                                                                                                                                                          | Estimation flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72                                                                                                   |

|    |                                            | 4.3.2.                                                                                                                                                                          | Library of circuit models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73                                                                                                   |

|    |                                            | 4.3.3.                                                                                                                                                                          | Composition analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75                                                                                                   |

|    |                                            | 4.3.4.                                                                                                                                                                          | The hardware complexity estimation tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 76                                                                                                   |

| 5. | Desi                                       | ign of C                                                                                                                                                                        | Custom Instructions for Coarse Grained Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31                                                                                                   |

|    | 5.1.                                       | Instruct                                                                                                                                                                        | ion Pattern Identification and Custom Instruction Composition 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33                                                                                                   |

|    |                                            | 5.1.1.                                                                                                                                                                          | Extraction of operation clusters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 84                                                                                                   |

|    |                                            | 5.1.2.                                                                                                                                                                          | Instruction pattern selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 89                                                                                                   |

|    |                                            | 5.1.3.                                                                                                                                                                          | Custom Instruction Composition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <del>)</del> 6                                                                                       |

|    | 5.2.                                       | Custom                                                                                                                                                                          | Instructions for Coarse Grained Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                      |

|    |                                            | 5.2.1.                                                                                                                                                                          | Description of custom instructions in CGADL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | )1                                                                                                   |

|    |                                            | 5.2.2.                                                                                                                                                                          | Integration of custom instructions in the application description 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                      |

|    |                                            | 5.2.3.                                                                                                                                                                          | Integration of custom processing elements in the architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                      |

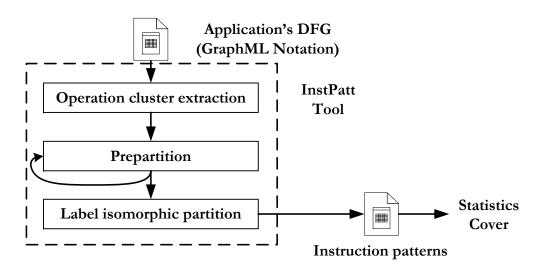

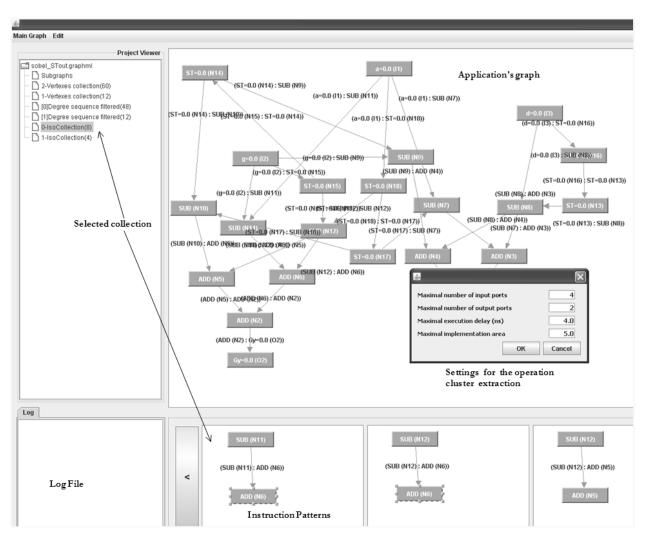

|    | 5.3.                                       |                                                                                                                                                                                 | ATT - A software tool for extraction of instruction patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                      |

|    |                                            | 5.3.1.                                                                                                                                                                          | The InstPatt flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | )6                                                                                                   |

|    |                                            |                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                      |

| 6. |                                            |                                                                                                                                                                                 | ts and Results 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                      |

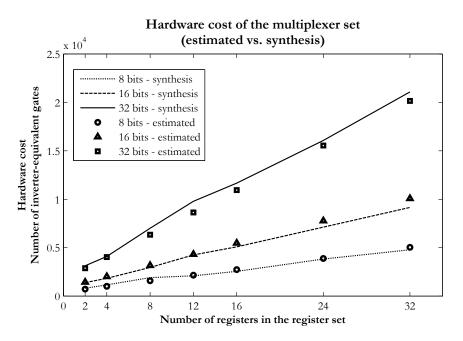

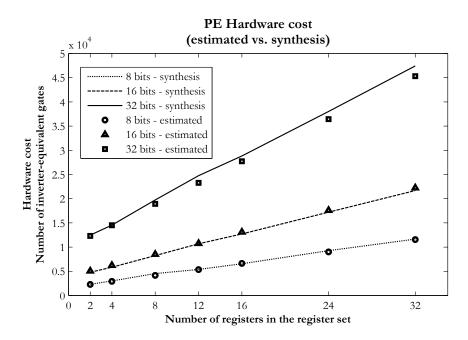

| 6. |                                            | A CGA                                                                                                                                                                           | DL-based software tool: estimation of hardware costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11                                                                                                   |

| 6. |                                            | A CGA<br>6.1.1.                                                                                                                                                                 | DL-based software tool: estimation of hardware costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11<br>12                                                                                             |

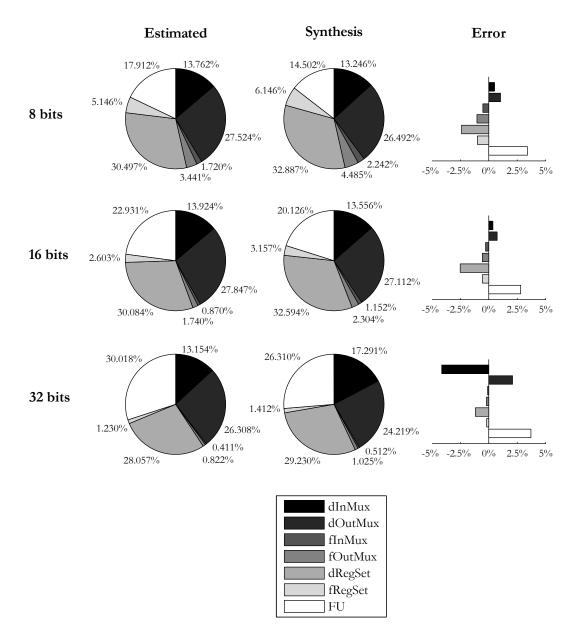

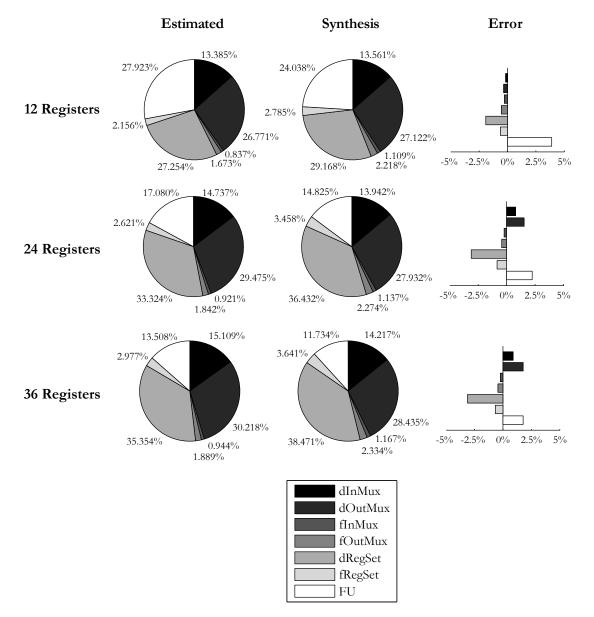

| 6. |                                            | A CGA<br>6.1.1.<br>6.1.2.                                                                                                                                                       | DL-based software tool: estimation of hardware costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11<br>12<br>13                                                                                       |

| 6. |                                            | A CGA<br>6.1.1.<br>6.1.2.<br>6.1.3.                                                                                                                                             | DL-based software tool: estimation of hardware costs       1         Experimental set up       1         Analysis of PE datapath composition       1         Scalability of the model       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11<br>12<br>13<br>17                                                                                 |

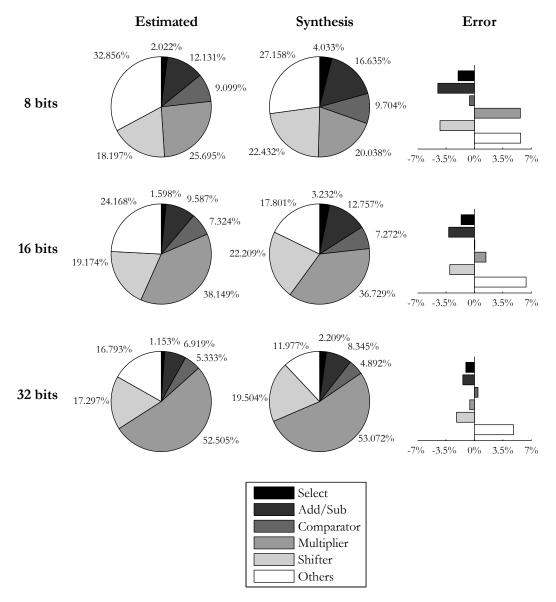

| 6. |                                            | A CGA<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.                                                                                                                                   | DL-based software tool: estimation of hardware costs       11         Experimental set up       11         Analysis of PE datapath composition       11         Scalability of the model       11         Comparison of implementation area       11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11<br>12<br>13<br>17<br>17                                                                           |

| 6. | 6.1.                                       | A CGA<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.                                                                                                                         | DL-based software tool: estimation of hardware costs       1         Experimental set up       1         Analysis of PE datapath composition       1         Scalability of the model       1         Comparison of implementation area       1         Discussion on the hardware costs estimation       1                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11<br>12<br>13<br>17<br>17<br>20                                                                     |

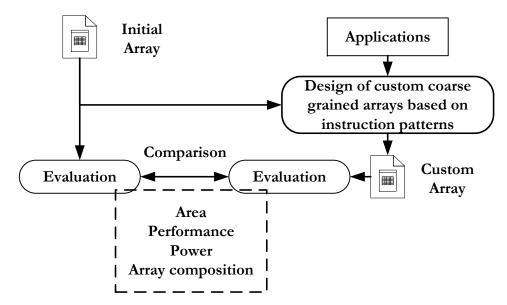

| 6. |                                            | A CGA<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>The im                                                                                                               | DL-based software tool: estimation of hardware costs       1         Experimental set up       1         Analysis of PE datapath composition       1         Scalability of the model       1         Comparison of implementation area       1         Discussion on the hardware costs estimation       1         pact of custom instruction sets on CGRAs       1                                                                                                                                                                                                                                                                                                                                                                                | 11<br>12<br>13<br>17<br>17<br>20<br>21                                                               |

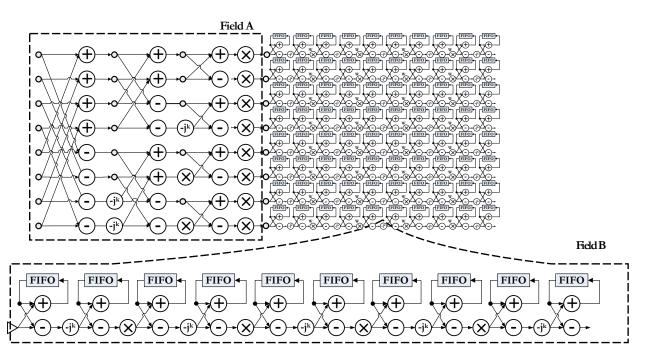

| 6. | 6.1.                                       | A CGA<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>The imp<br>6.2.1.                                                                                                    | DL-based software tool: estimation of hardware costs       1         Experimental set up       1         Analysis of PE datapath composition       1         Scalability of the model       1         Comparison of implementation area       1         Discussion on the hardware costs estimation       1         Pact of custom instruction sets on CGRAs       1         Custom architecture for scalable OFDMA based systems       1                                                                                                                                                                                                                                                                                                           | 11<br>12<br>13<br>17<br>17<br>20<br>21<br>23                                                         |

| 6. | 6.1.                                       | A CGA<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>The im                                                                                                               | DL-based software tool: estimation of hardware costs       1         Experimental set up       1         Analysis of PE datapath composition       1         Scalability of the model       1         Comparison of implementation area       1         Discussion on the hardware costs estimation       1         pact of custom instruction sets on CGRAs       1                                                                                                                                                                                                                                                                                                                                                                                | 11<br>12<br>13<br>17<br>17<br>20<br>21<br>23                                                         |

|    | 6.1.                                       | A CGA<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>The imp<br>6.2.1.                                                                                                    | DL-based software tool: estimation of hardware costs       1         Experimental set up       1         Analysis of PE datapath composition       1         Scalability of the model       1         Comparison of implementation area       1         Discussion on the hardware costs estimation       1         Discussion on the hardware costs estimation       1         Custom architecture for scalable OFDMA based systems       1         Computer vision for automotive applications       1                                                                                                                                                                                                                                            | 11<br>12<br>13<br>17<br>17<br>20<br>21<br>23<br>33                                                   |

| 7. | 6.1.<br>6.2.<br>Con                        | A CGA<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>The imp<br>6.2.1.<br>6.2.2.                                                                                          | DL-based software tool: estimation of hardware costs       11         Experimental set up       11         Analysis of PE datapath composition       11         Scalability of the model       11         Comparison of implementation area       11         Discussion on the hardware costs estimation       11         Discussion of instruction sets on CGRAs       12         Custom architecture for scalable OFDMA based systems       12         Computer vision for automotive applications       13         13       14                                                                                                                                                                                                                   | 11<br>12<br>13<br>17<br>17<br>20<br>21<br>23<br>33<br><b>45</b>                                      |

| 7. | 6.1.<br>6.2.<br>Con                        | A CGA<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>The im<br>6.2.1.<br>6.2.2.<br>clusion<br>endix /                                                                     | DL-based software tool: estimation of hardware costs       11         Experimental set up       11         Analysis of PE datapath composition       11         Scalability of the model       11         Comparison of implementation area       11         Discussion on the hardware costs estimation       12         pact of custom instruction sets on CGRAs       12         Computer vision for automotive applications       13         13       14         14       14                                                                                                                                                                                                                                                                    | 11<br>12<br>13<br>17<br>17<br>20<br>21<br>23<br>33<br>45<br>49                                       |

| 7. | 6.1.<br>6.2.<br>Con<br>App<br>A.1.         | A CGA<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>The im<br>6.2.1.<br>6.2.2.<br>clusion<br>endix <i>A</i><br>CGAD                                                      | DL-based software tool: estimation of hardware costs       11         Experimental set up       11         Analysis of PE datapath composition       11         Scalability of the model       11         Comparison of implementation area       11         Discussion on the hardware costs estimation       11         Discussion of instruction sets on CGRAs       12         Custom architecture for scalable OFDMA based systems       12         Computer vision for automotive applications       13         13       14                                                                                                                                                                                                                   | 11<br>12<br>13<br>17<br>17<br>20<br>21<br>23<br>33<br><b>15</b><br><b>19</b><br>49                   |

| 7. | 6.1.<br>6.2.<br>Con<br>App<br>A.1.<br>A.2. | A CGA<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>The im<br>6.2.1.<br>6.2.2.<br><b>clusion</b><br>endix <i>A</i><br>CGAD<br>CGAD<br>Circuit                            | DL-based software tool: estimation of hardware costs       11         Experimental set up       11         Analysis of PE datapath composition       11         Scalability of the model       11         Comparison of implementation area       11         Discussion on the hardware costs estimation       11         Discussion on the hardware costs estimation       11         Discussion on the hardware costs estimation       12         Deact of custom instruction sets on CGRAs       12         Computer vision for automotive applications       12         Is       14         L keywords and symbols       14         L grammar production rules - EBNF       14         models and hardware complexity estimation costs       14 | 11<br>12<br>13<br>17<br>20<br>21<br>23<br>33<br><b>15</b><br><b>19</b><br>49<br>49<br>52             |

| 7. | 6.1.<br>6.2.<br>Con<br>App<br>A.1.<br>A.2. | A CGA<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>The im<br>6.2.1.<br>6.2.2.<br><b>clusior</b><br><b>endix</b> <i>A</i><br>CGAD<br>CGAD<br>Circuit<br>A.3.1.           | DL-based software tool: estimation of hardware costs       11         Experimental set up       11         Analysis of PE datapath composition       11         Scalability of the model       11         Comparison of implementation area       11         Discussion on the hardware costs estimation       12         pact of custom instruction sets on CGRAs       12         Custom architecture for scalable OFDMA based systems       12         Computer vision for automotive applications       13         Is       14         L keywords and symbols       14         L grammar production rules - EBNF       14         Multiplexer Block       14                                                                                    | 11<br>12<br>13<br>17<br>17<br>20<br>21<br>23<br>33<br><b>15</b><br><b>19</b><br>49<br>49<br>52<br>52 |

| 7. | 6.1.<br>6.2.<br>Con<br>App<br>A.1.<br>A.2. | A CGA<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>The im<br>6.2.1.<br>6.2.2.<br><b>clusion</b><br><b>endix</b> <i>A</i><br>CGAD<br>CGAD<br>Circuit<br>A.3.1.<br>A.3.2. | DL-based software tool: estimation of hardware costs       11         Experimental set up       11         Analysis of PE datapath composition       11         Scalability of the model       11         Comparison of implementation area       11         Discussion on the hardware costs estimation       12         pact of custom instruction sets on CGRAs       12         Custom architecture for scalable OFDMA based systems       12         Computer vision for automotive applications       14         L keywords and symbols       14         L grammar production rules - EBNF       14         Multiplexer Block       14         Finite state machine block       14                                                            | 11<br>12<br>13<br>17<br>20<br>21<br>23<br>33<br><b>15</b><br><b>19</b><br>49<br>49<br>52<br>52<br>52 |

| 7. | 6.1.<br>6.2.<br>Con<br>App<br>A.1.<br>A.2. | A CGA<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>The im<br>6.2.1.<br>6.2.2.<br><b>clusion</b><br><b>endix</b> <i>A</i><br>CGAD<br>CGAD<br>Circuit<br>A.3.1.<br>A.3.2. | DL-based software tool: estimation of hardware costs       11         Experimental set up       11         Analysis of PE datapath composition       11         Scalability of the model       11         Comparison of implementation area       11         Discussion on the hardware costs estimation       12         pact of custom instruction sets on CGRAs       12         Custom architecture for scalable OFDMA based systems       12         Computer vision for automotive applications       13         Is       14         L keywords and symbols       14         L grammar production rules - EBNF       14         Multiplexer Block       14                                                                                    | 11<br>12<br>13<br>17<br>20<br>21<br>23<br>33<br><b>15</b><br><b>19</b><br>49<br>49<br>52<br>52<br>52 |

# **List of Figures**

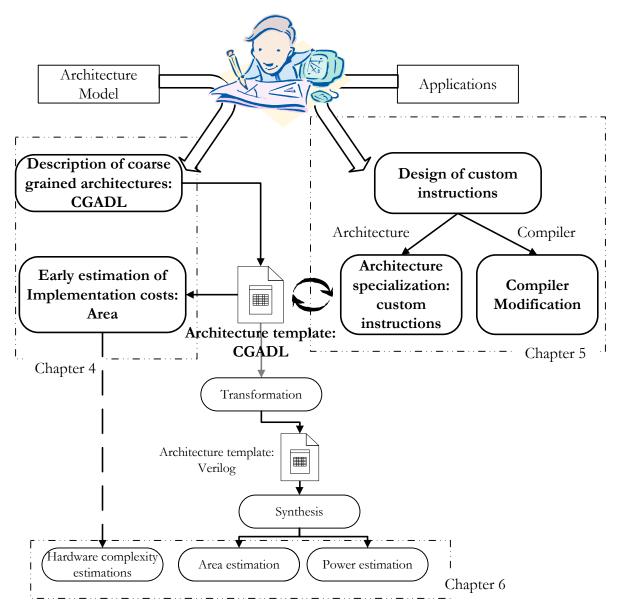

| 1.1.         | Design flow proposed in this work for the development of CGRAs                                                                                                                                                                                                              | 6        |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

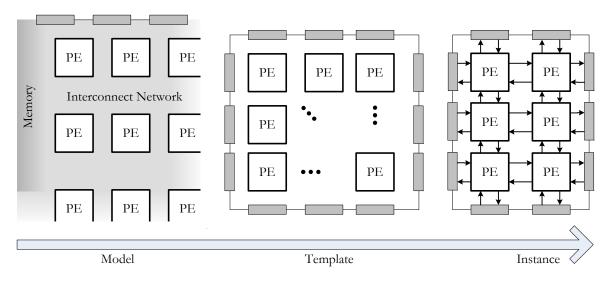

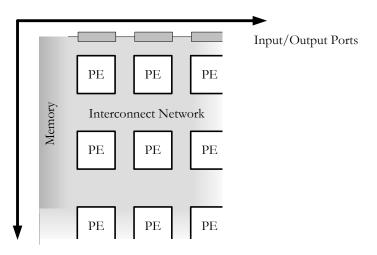

| 2.1.<br>2.2. | General design flow for coarse-grained reconfigurable architectures                                                                                                                                                                                                         | 10<br>10 |

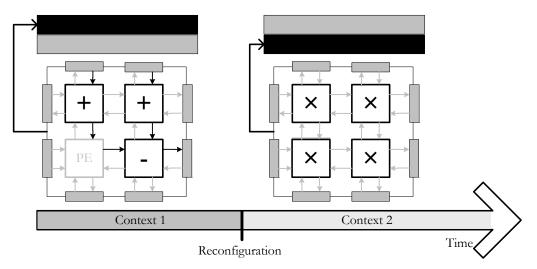

| 2.3.         | <i>Reconfiguration</i> in the CRC model. A <i>context</i> defines the functionality of each PE and the flow of data between PEs. Reconfiguration takes place by choosing another context in the context memory.                                                             | 11       |

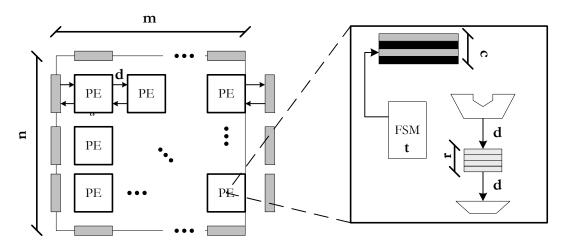

| 2.4.         | Parameterization in the CRC model. n and m determine the number of rows and the number of columns in the array; d determines the datapath width; c, the number                                                                                                              | 11       |

|              | e                                                                                                                                                                                                                                                                           | 13       |

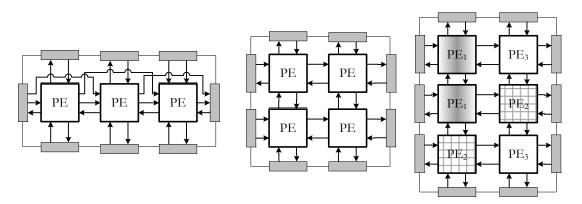

| 2.5.         | Examples of architecture instances for the CRC model: (a) Line architecture with 3 PEs connected with a 0-1-hop network; (b) 2x2 array of PEs connected with the                                                                                                            |          |

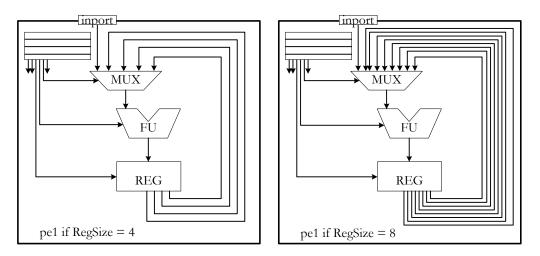

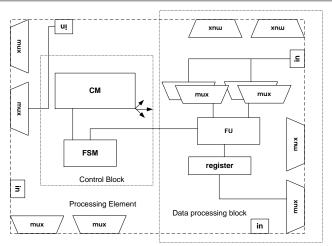

| 2.6.         | nearest neighbor; (c) 3x2 array with different PE types                                                                                                                                                                                                                     | 14       |

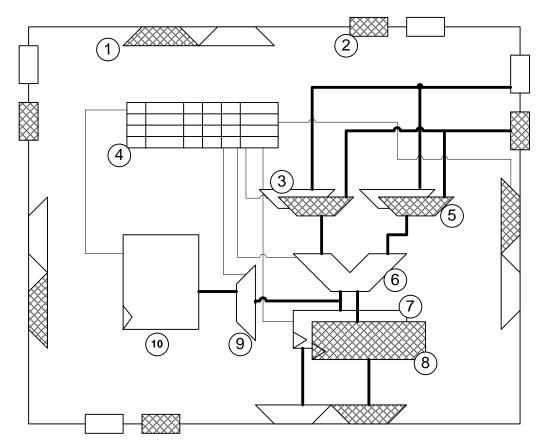

|              | tiplexers; (4) context memory; (6) functional unit; (7,8) registers; (10) finite state machine;                                                                                                                                                                             | 15       |

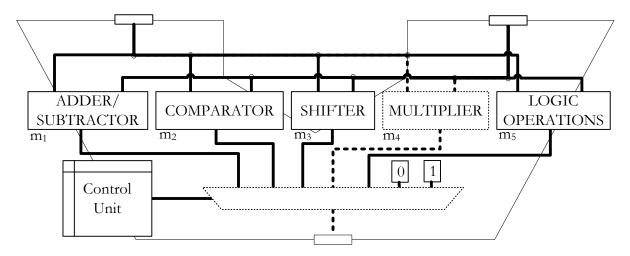

| 2.7.         | A basic functional unit. During the execution of an <i>instruction</i> , the control unit ac-<br>tivates exactly the necessary operation module to carry out the desired data trans-<br>formation. Control units also control the multiplexers to select the result(s) that |          |

| •            | will be presented in the output port(s).                                                                                                                                                                                                                                    | 17       |

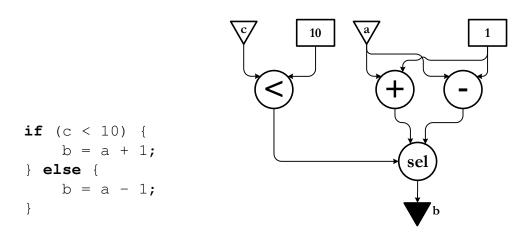

| 2.8.<br>2.9. | Transformation of if-else structures in a pure data flow. Both branches are executed producing data. Then a select operation chooses the data to be used                                                                                                                    | 21       |

| 2 10         | <b>e</b> 1                                                                                                                                                                                                                                                                  | 22<br>23 |

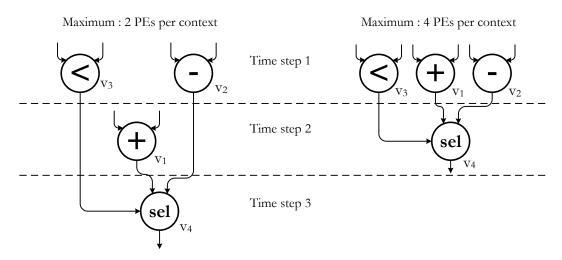

|              | Scheduling examples                                                                                                                                                                                                                                                         | 25       |

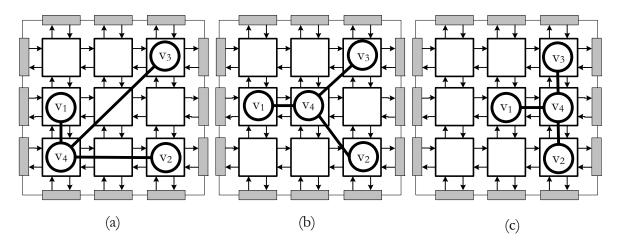

|              | state with minimal network obtained after successive improvements                                                                                                                                                                                                           | 24       |

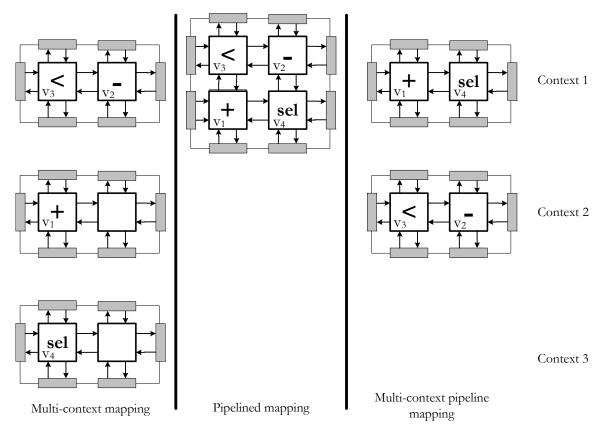

| 2.12.        | Multi-context, pipeline, and multi-context pipeline                                                                                                                                                                                                                         | 25       |

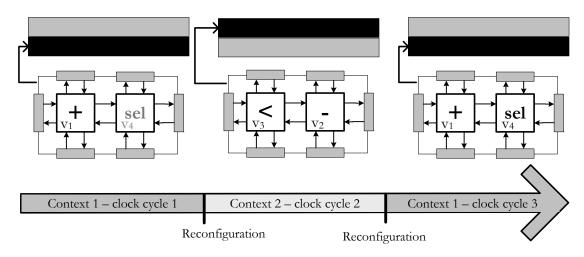

| 2.13.        | Example for the execution of the multi-context pipeline.                                                                                                                                                                                                                    | 26       |

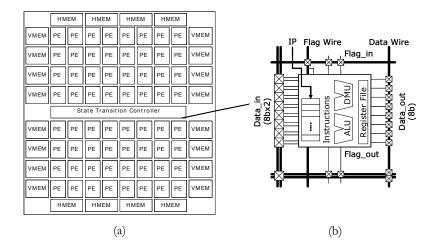

| 3.1.<br>3.2. | Array organization and PE circuit in NEC's DRP. Source [84] Block diagram of the ULIW architecture from Silicon Hive. The number of processing and storage elements(PSEs), registers, FUs, and data memory is config-                                                       | 28       |

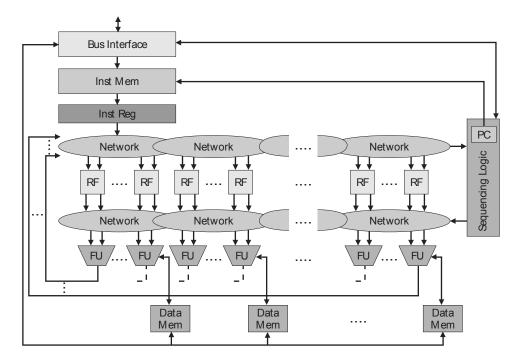

|              | urable during the design phase. Source [51]                                                                                                                                                                                                                                 | 30       |

## List of Figures

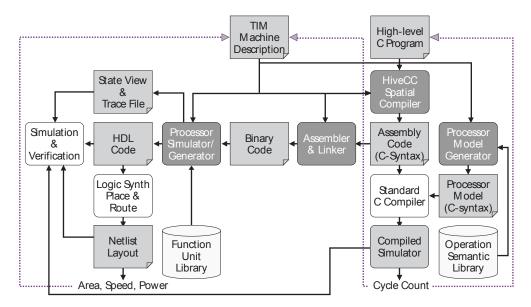

| 3.3.  | Design flow used by costumers of Silicon Hive. The starting point of the design flow is the proprietary language TIM. From this description a Processor simulator, VHDL (or Verilog) code, and a compiler are automatically generated. Source [51].                                                                                                                                                                                                      | 31 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

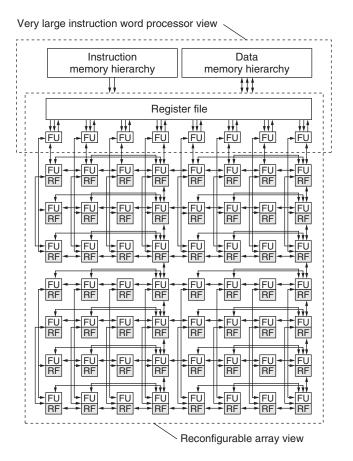

| 3.4.  | Instance of the ADRES architecture template. The ADRES couples a VLIW pro-                                                                                                                                                                                                                                                                                                                                                                               |    |

|       | cessor with a reconfigurable array. Source [75]                                                                                                                                                                                                                                                                                                                                                                                                          | 32 |

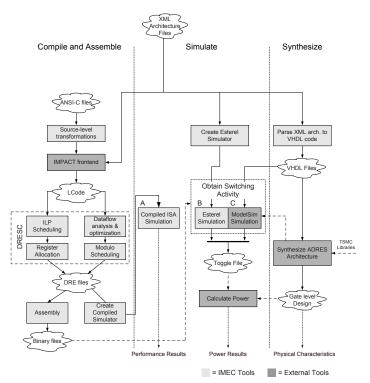

| 3.5.  | ADRES software-tool flow: an extensive CAD support for the design phase, which includes compiler, simulator, and synthesis. Source [15]                                                                                                                                                                                                                                                                                                                  | 33 |

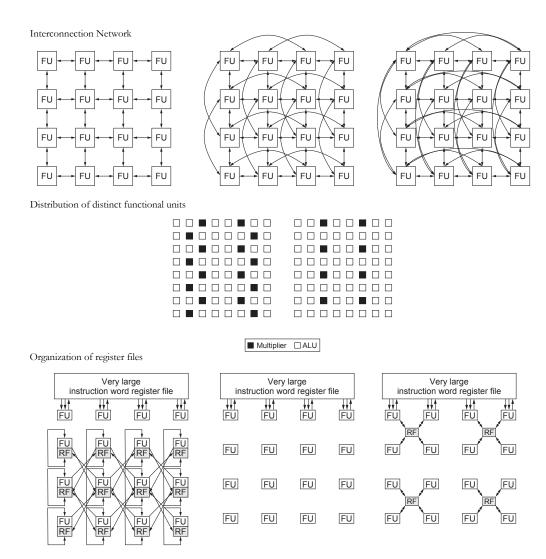

| 3.6.  | Possible configurations for the ADRES interconnection network, disposition of different functional units, and organization of register files. Many more are available in the ADRES template library. Source [75].                                                                                                                                                                                                                                        | 35 |

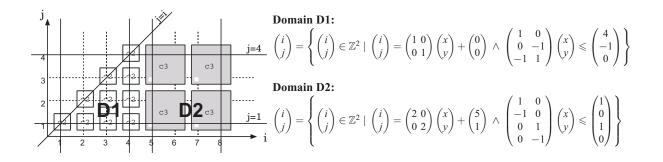

| 3.7.  | MAML's polytope domains representation. In MAML, the designer can assign positions in a 2D space to the PEs. Later, PEs can be referred to by using this                                                                                                                                                                                                                                                                                                 |    |

|       | positioning system. Source [68].                                                                                                                                                                                                                                                                                                                                                                                                                         | 37 |

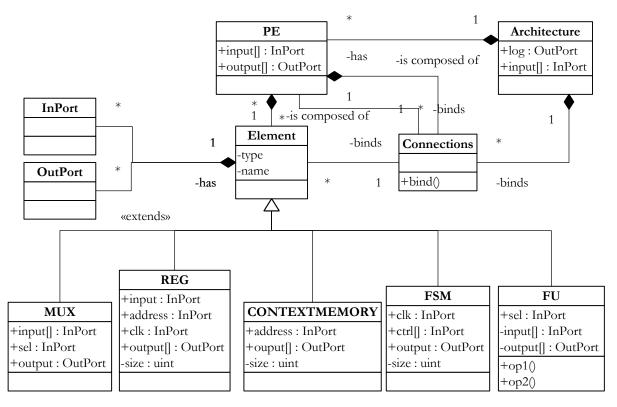

| 4.1.  | UML diagram for the semantic model of CGADL.                                                                                                                                                                                                                                                                                                                                                                                                             | 49 |

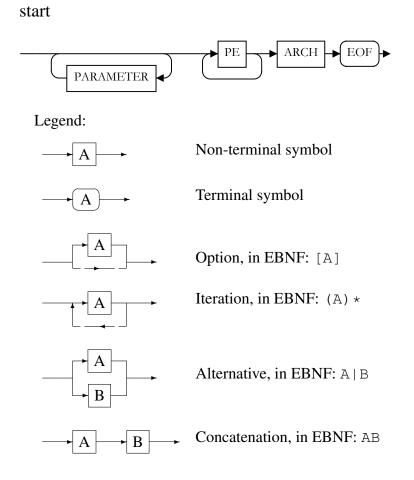

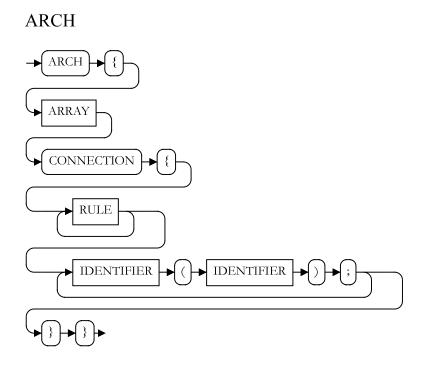

| 4.2.  | Starting syntax diagram for a CGADL description. This diagram corresponds to the production of the start symbol in a EBNF notation. To read syntax diagrams, follow the arrows from left to right. Branches are possible divergent paths and only one of them should be followed at a time. A non-terminal symbol (rectangular box) represents a production rule by itself. A terminal symbol (rounded box) represents a language keyword oder a symbol. | 50 |

| 1 2   |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

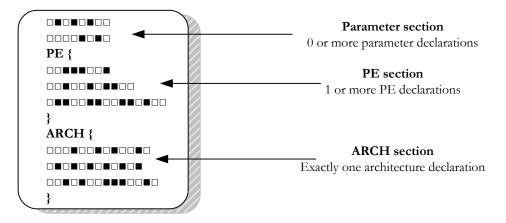

| 4.3.  | Structure of a CGADL description file                                                                                                                                                                                                                                                                                                                                                                                                                    | 51 |

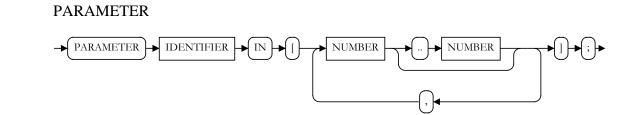

| 4.4.  | Syntax diagram for a PARAMETER section.                                                                                                                                                                                                                                                                                                                                                                                                                  | 52 |

| 4.5.  | Example of a PARAMETER section.                                                                                                                                                                                                                                                                                                                                                                                                                          | 52 |

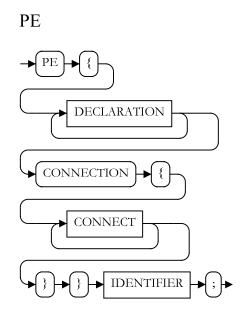

| 4.6.  | Syntax diagram of the PE section.                                                                                                                                                                                                                                                                                                                                                                                                                        | 53 |

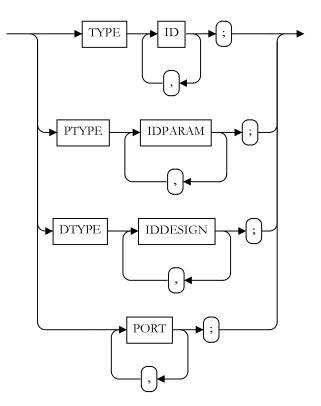

| 4.7.  | Syntax diagram of the declaration section.                                                                                                                                                                                                                                                                                                                                                                                                               | 54 |

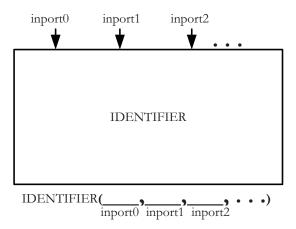

| 4.8.  | Generic schema for the connections of a CGADL element.                                                                                                                                                                                                                                                                                                                                                                                                   | 55 |

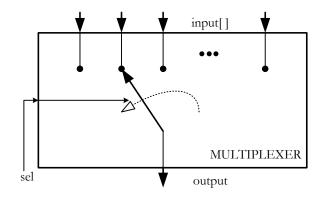

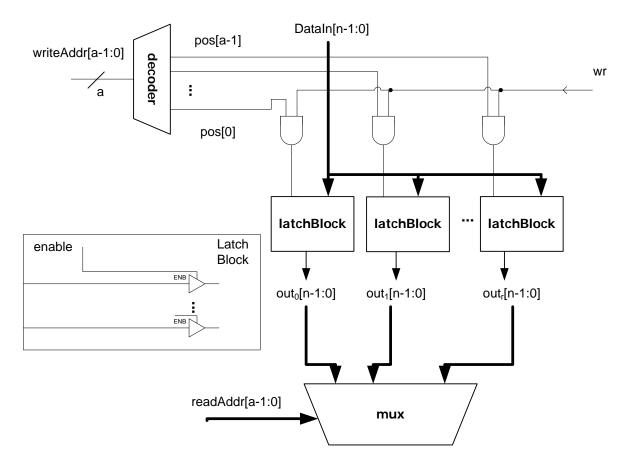

| 4.9.  | Model of a multiplexer (MUX) in CGADL.                                                                                                                                                                                                                                                                                                                                                                                                                   | 56 |

|       | Example of a multiplexer declaration and connection.                                                                                                                                                                                                                                                                                                                                                                                                     | 57 |

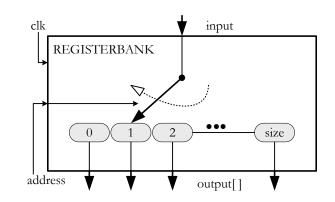

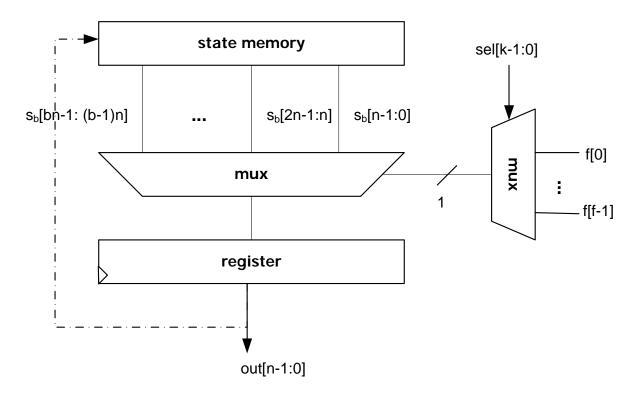

|       | Semantic model of a register set (REG) in CGADL.                                                                                                                                                                                                                                                                                                                                                                                                         | 58 |

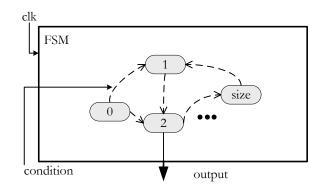

|       | Semantic model of a finite state machine (FSM) in CGADL.                                                                                                                                                                                                                                                                                                                                                                                                 | 58 |

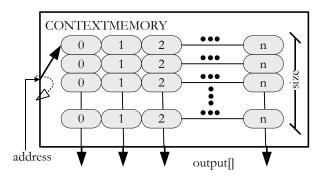

|       | Semantic model of a context memory (CONTEXTMEMORY) in CGADL                                                                                                                                                                                                                                                                                                                                                                                              | 59 |

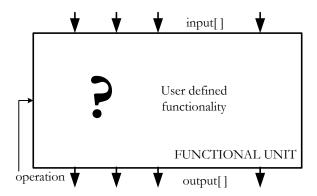

|       | Semantic model of a functional unit (FU) in CGADL.                                                                                                                                                                                                                                                                                                                                                                                                       | 60 |

|       | An example for the description of operation's behavior. In this work, the program-<br>ming language C is used to describe the behavior of FU's operations                                                                                                                                                                                                                                                                                                | 61 |

| 4.16. | CGADL description and schematic diagram of the PE <i>Bianca</i>                                                                                                                                                                                                                                                                                                                                                                                          | 63 |

| 4.17. | Positional model for the distribution of PEs in the architecture: an array-like struc-                                                                                                                                                                                                                                                                                                                                                                   |    |

|       | ture. A $2 \times 3$ architecture instance is depicted on the grid; every position has exactly                                                                                                                                                                                                                                                                                                                                                           |    |

|       | one PE, which can be uniquely identified using the positioning system                                                                                                                                                                                                                                                                                                                                                                                    | 64 |

|       | . Syntax diagram of the ARCH section.                                                                                                                                                                                                                                                                                                                                                                                                                    | 64 |

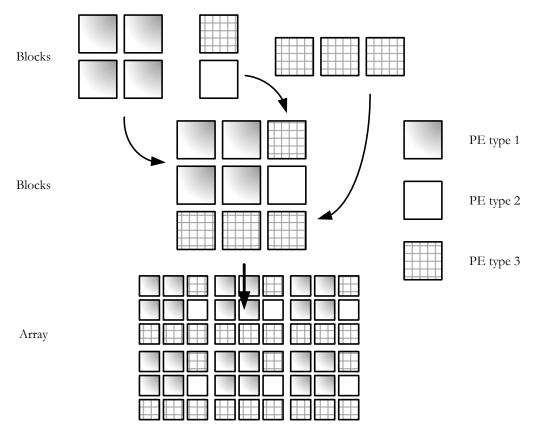

|       | Composition of a regular array based on blocks.                                                                                                                                                                                                                                                                                                                                                                                                          | 66 |

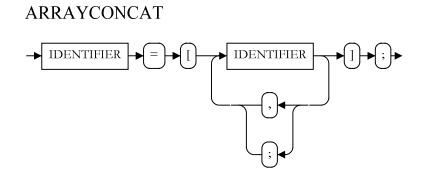

| 4.20. | . Syntax diagram for the array declaration                                                                                                                                                                                                                                                                                                                                                                                                               | 66 |

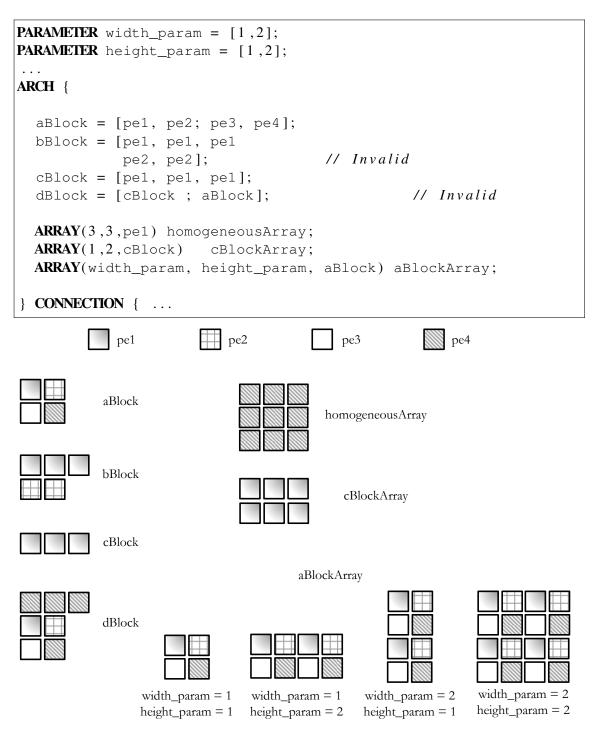

| 4.21. | Declaration of blocks and arrays in the ARCH section: examples. The <i>aBlockArray</i> is a template, which can generate up to 4 different instances depending on the values of <i>width_param</i> and <i>height_param</i>                                                                                                                                                                                                                  | 68       |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

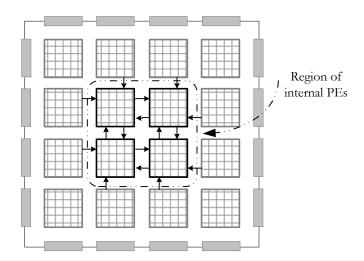

| 4.22. | Description of the interconnection network topology based on a region. Regions are groups of PEs that are connected in the same way. For example, all internal PEs in this array are connected in the same way: internal PEs build up a <i>region</i> that abide by the same interconnection <i>rules</i> . CGADL uses this concept to describe the interconnection network. The design of an interconnection topology based on             |          |

| 4.23. | regions and rules is an innovative feature introduced by this work                                                                                                                                                                                                                                                                                                                                                                          | 69       |

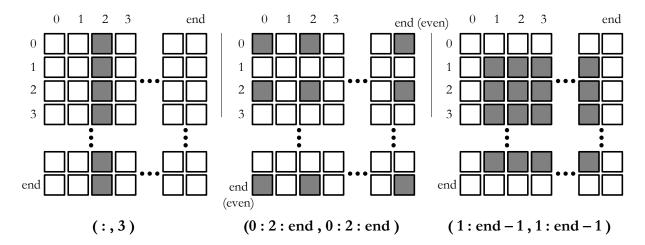

|       | shown in the third example                                                                                                                                                                                                                                                                                                                                                                                                                  | 69       |

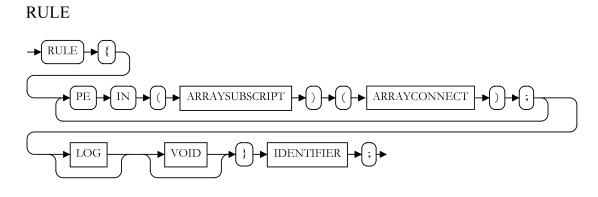

|       | Syntax diagram of a connection rule.                                                                                                                                                                                                                                                                                                                                                                                                        | 70       |

|       | Example of a CONNECTION-RULE section.                                                                                                                                                                                                                                                                                                                                                                                                       | 70       |

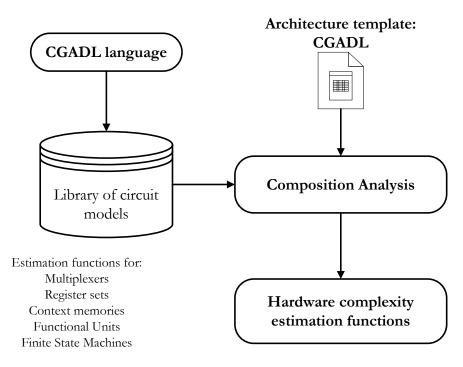

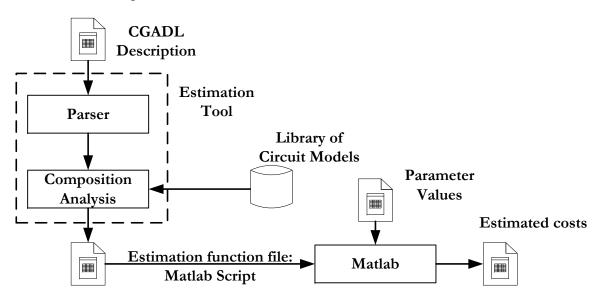

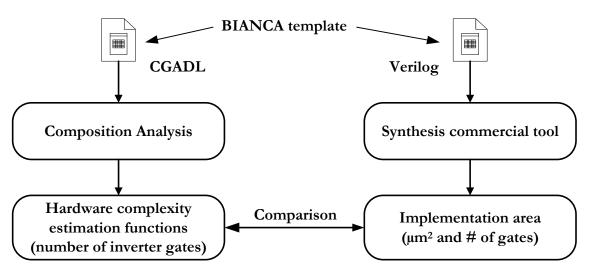

|       | Workflow for the hardware complexity analysis method.                                                                                                                                                                                                                                                                                                                                                                                       | 73       |

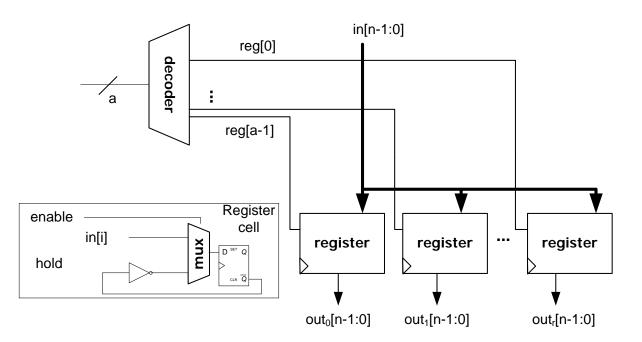

|       | Circuit model for hardware cost estimation of a register set                                                                                                                                                                                                                                                                                                                                                                                | 74       |

|       | Workflow of the hardware cost estimation software tool                                                                                                                                                                                                                                                                                                                                                                                      | 77<br>78 |

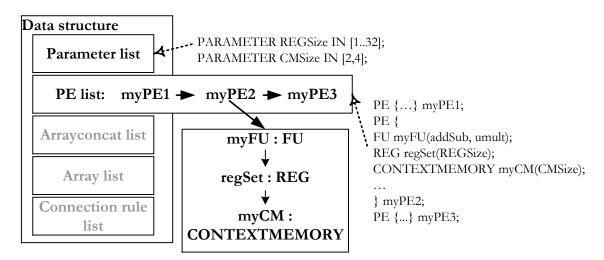

|       | Intermediate format generated by the CGADL parser                                                                                                                                                                                                                                                                                                                                                                                           | 70       |

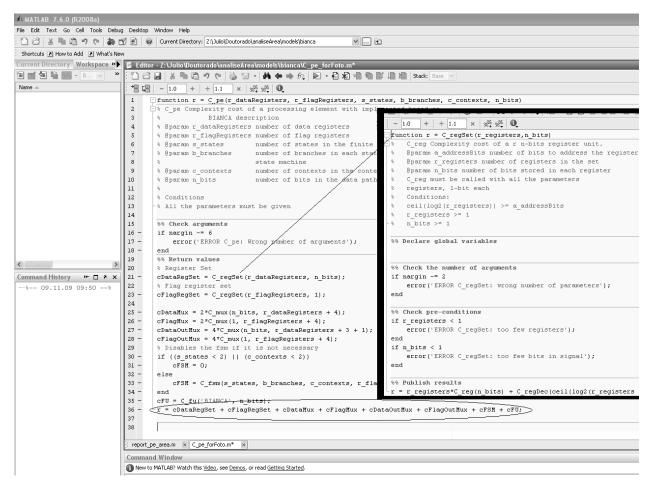

|       | (C_RegSet) from the library of circuit models. Compare with value in table 4.3                                                                                                                                                                                                                                                                                                                                                              | 79       |

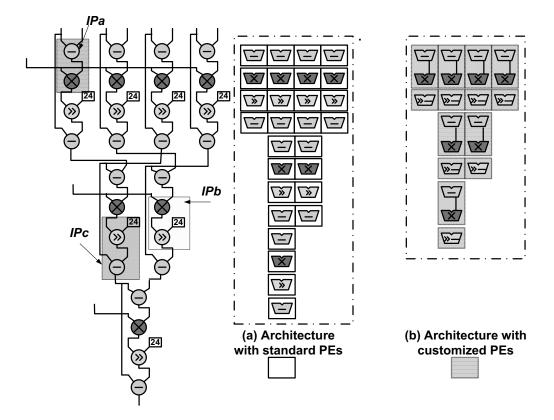

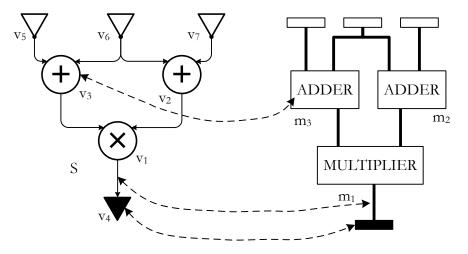

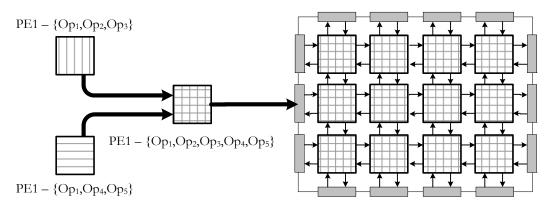

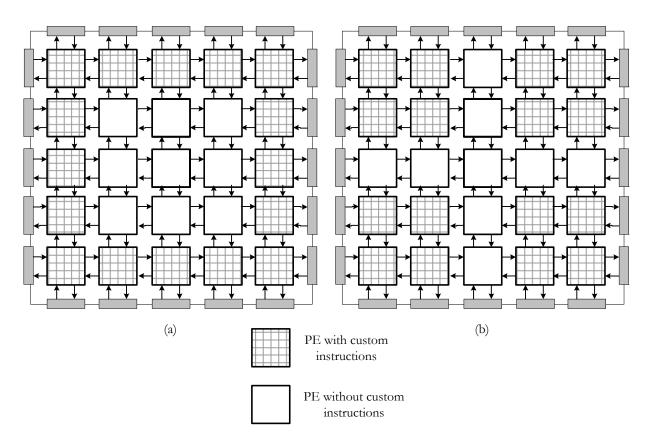

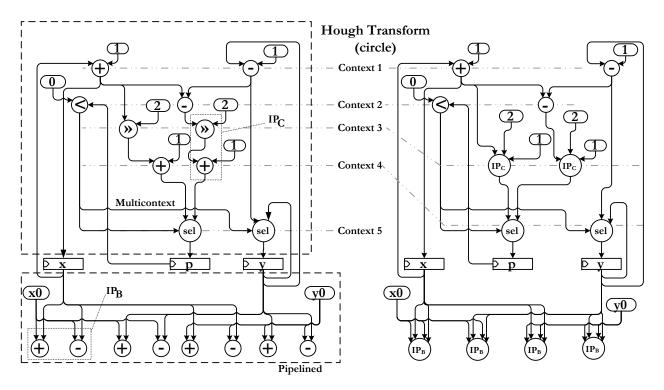

| 5.1.  | Trilinear Interpolation mapping on architectures with (a) standard and (b) customized PEs                                                                                                                                                                                                                                                                                                                                                   | 82       |

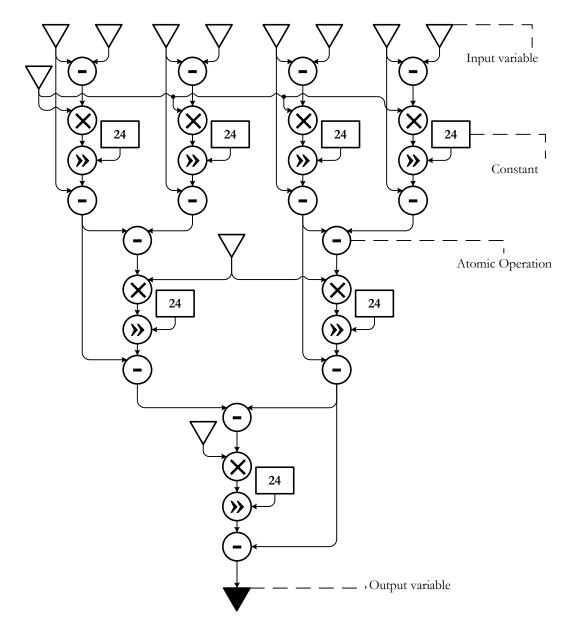

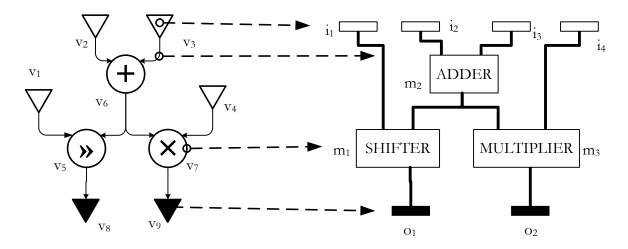

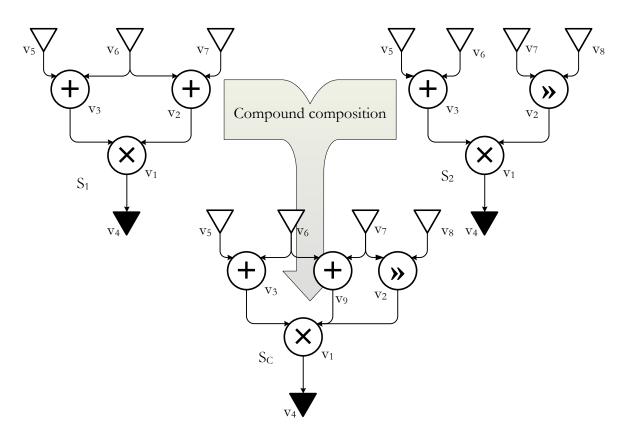

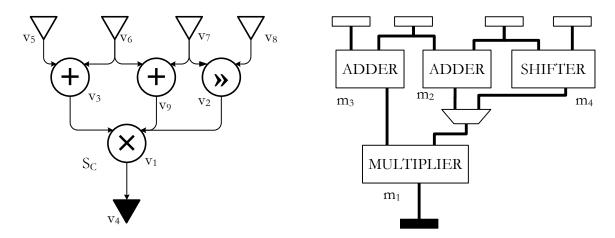

| 5.2.  | DFGs can be seen as the description of a datapath: input operations $(\{v_1, v_2, v_3, v_4\})$ are mapped to input ports $(\{i_1, i_2, i_3, i_4\})$ ; output operations $(\{v_8, v_9\})$ correspond to output ports $(\{o_1, o_2\})$ ; atomic operations $(\{v_5, v_6, v_7\})$ represent operation modules $(\{m_1, m_2, m_3\})$ ; and edges correspond to data transfer lines between modules and/or ports.                                | 83       |

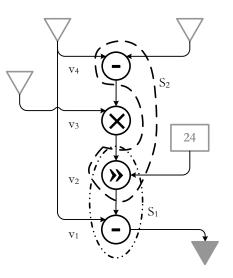

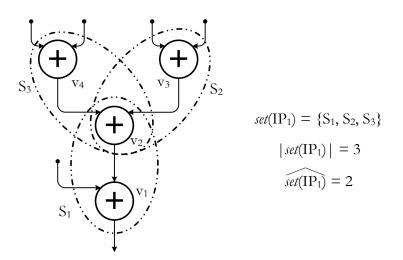

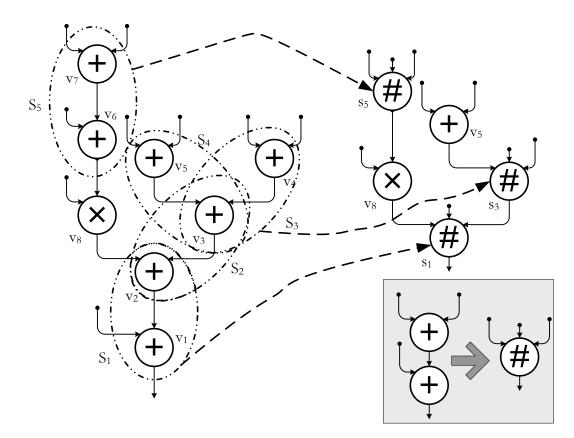

| 5.3.  | Operation clusters in a DFG. $S_1$ is the subgraph induced by $\{v_1, v_2\}$ . It is convex, consumes three input values (IN( $S_1$ ) = 3) and produces one output value (OUT( $S_1$ ) = 1). Its estimated implementation cost is $C(S_1) = C(v_1) + C(v_2)$ , and its estimated execution delay is $\delta(S_1) = \delta(v_1) + \delta(v_2)$ . $S_2$ is a non-convex                                                                       | 05       |

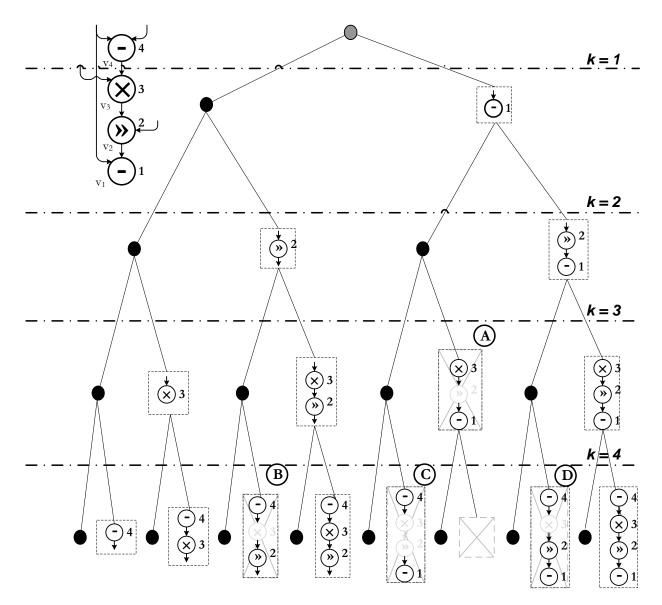

| 5.4.  | cluster induced by $\{v_2, v_4\}$<br>Binary search tree for the extraction of feasible operation clusters of the depicted DFG. Constraints are $N_{\text{out}} = 1$ , $N_{\text{in}} = 4$ , $C_{\text{max}} = \infty$ , and $\delta_{\text{max}} = \infty$ . Each branching level k considers the exclusion (left branch) or the inclusion (right branch) of the node numbered as k. Crossed boxes indicate operation clusters that violate | 85       |

|       | some constraint: node (A) produces more than 2 output values; and nodes (A), (B),                                                                                                                                                                                                                                                                                                                                                           |          |

|       | (C), and (D) are not convex.                                                                                                                                                                                                                                                                                                                                                                                                                | 87       |

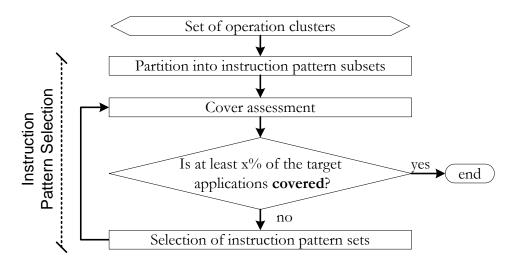

| 5.5.  | Activity flow proposed to select which instruction patterns should be implemented as custom instructions.                                                                                                                                                                                                                                                                                                                                   | 90       |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

vii

| 5.6.         | Operation clusters with common operation vertices: only one cluster at a time may be mapped to a custom instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

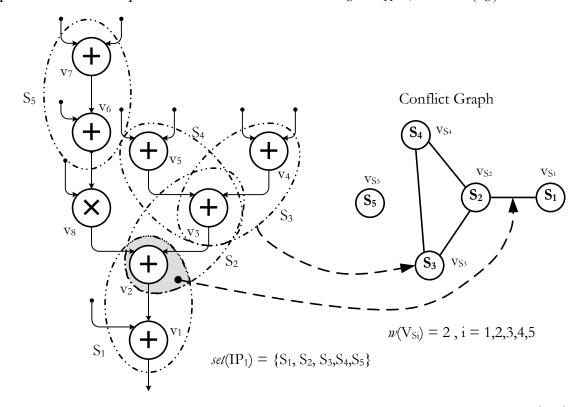

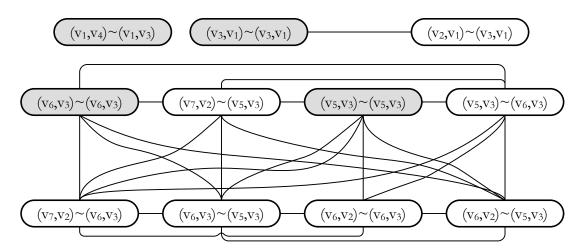

| 5.7.         | Building the conflict graph for the instruction pattern set $set(IP) = \{S_1, S_2, S_3, S_4, S_5\}$ :<br>Vertices $v_{S_1}, v_{S_2}, v_{S_3}, v_{S_4}$ , and $v_{S_5}$ represent the operation clusters $S_1, S_2, S_3, S_4$ ,<br>and $S_5$ , respectively. $v_{S_1}$ and $v_{S_2}$ are connected because they have $v_2$ as a common<br>vertex. $v_{S_2}, v_{S_3}$ and $v_{S_4}$ are interconnected because there is a conflict in $v_3$ . Oper-<br>ation cluster $S_5$ does not have a conflict with any other operation cluster, therefore<br>$v_{S_5}$ has no edges |

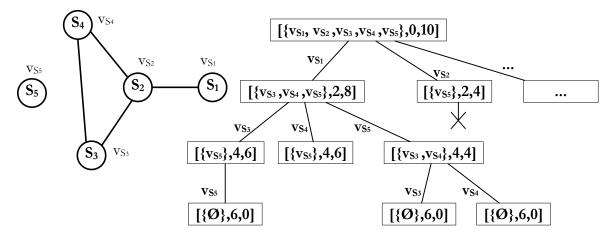

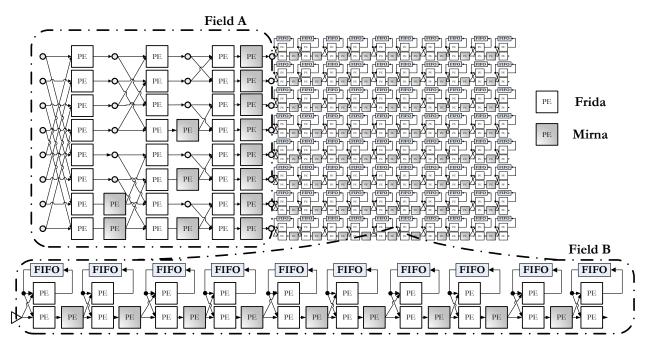

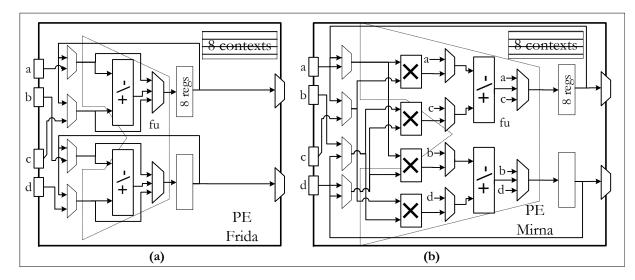

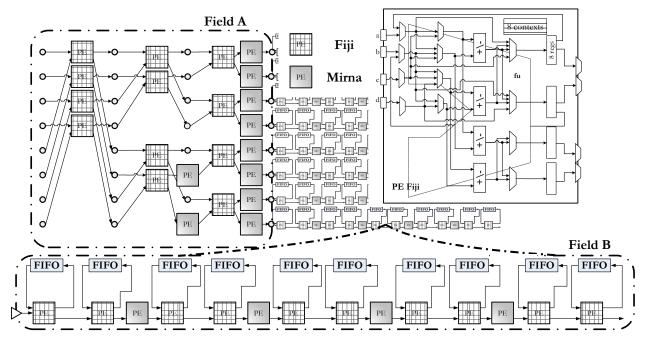

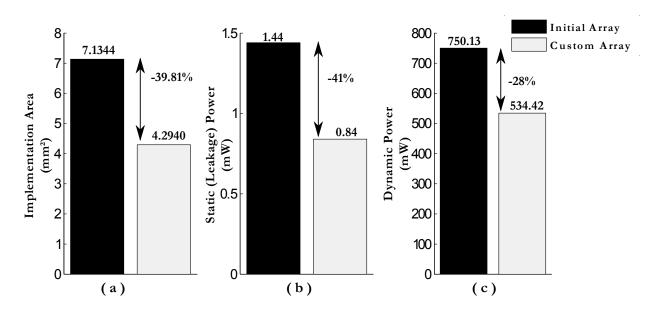

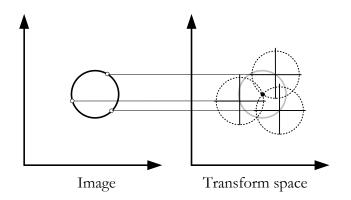

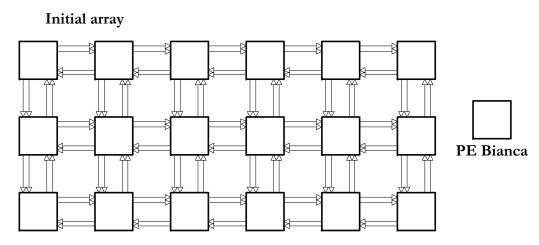

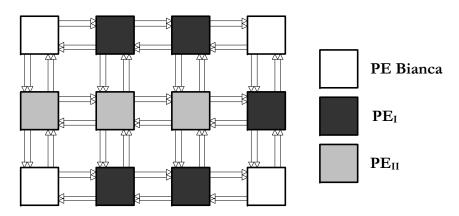

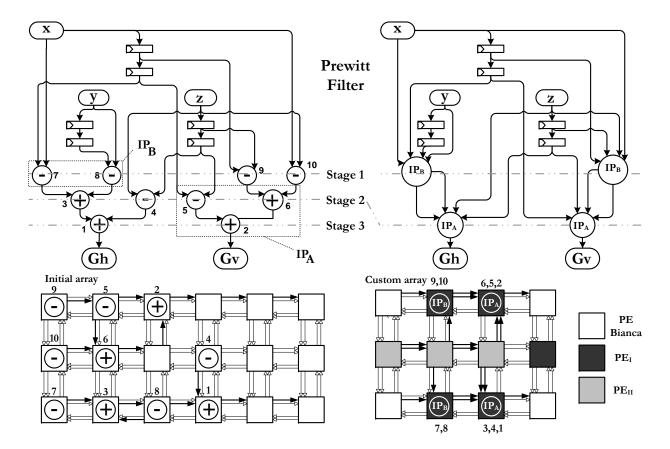

| 5.8.         | Calculating the cover of $set(IP) = \{S_1, S_2, S_3, S_4, S_5\}$ , for the example DFG depicted in Figure 5.7. This search tree is generated executing the Algorithm 2 to the example conflict graph. The conflict graph is repeated here to ease the understanding. Each node is depicted as a tuple $[\{v_1, v_2, \dots, v_k\}, a_w^*, a_w^* + w(V^*)]$ , representing the nodes not yet considered in the stable set, the actual accumulated weight up to this node, and the upper bound to the weight that can be achieved by the underlying subtree                |